[Lecture - OS] 02. Hardware

[Lecture - OS] Hardware

Agenda

- Computer Systems Architecture

- Interrupt Mechanism

- Hardware Protection

1. Computer Systems Architecture

Components inside Computer

Processing Unit (Control/ALU)

- 프로그램의 지시에 따라 여러 요소들을 제어하기 위한 processor의 요소다.

Memory

- 동작하는 program이나 data를 보호하기 위한 storage area

Input/Output

- User-Interface Devices

- Display, Keyboard, Mouse, etc,.

- Storage Devices

- Hard disk, CD/DVD, flash, etc,.

- Network Adapters

- 다른 컴퓨터와 의사소통을 위해 존재

Data path

- 데이터 전송 및 components 끼리 동작을 위해 존재하는 Pathway.

- System interrupt나 System bus로도 불린다.

Representation of Data

Bites/Bytes

- Bit는 Binary Digit의 줄임말이다.

- n bits = $2^n$

- 1 bytes = 8 bits(size of char)

- n bytes = $2^{8 * n}$

Word

- 32bit machine 환경에서 32-bit data를 의미한다.

- 기초적인 데이터 단위다.

- Register의 크기다!

Numbers

System Bus

read/write transaction을 수행한다.

tansaction은 DB에서 더 이상 쪼갤 수 없고, 간섭이 불가능한 데이터를 의미한다.

오류가 나면 동작을 거꾸로 수행한다.(Commit or Abort)

- Computer system의 주요 components를 연결한다.

- 아래와 같은 타입이 있다.

- Data bus

- Bus master와 slave 사이 data 경로

- Address bus

- Data 전송의 target location을 특정한다.

- Control bus

- CPU로부터 명령과 devices의 contrller로부터 status signal을 운반한다.

- Data bus

- Two types of bus transaction

- Read/Write

- Read and Write를 할 때도 있지만(Multiprocessor Sync), 대부분은 bus 점유 문제 때문에 둘 중 하나만 수행한다.

Bus Arbiter

Bus master가 control bus를 통해 요청을 보내면 우선순위에 따라 grant signal을 보낸다.

- 여러 bus들의 요청 사이 충돌을 조율한다.

- Hand Shaking 과정

- Accept bus request signal

- Replies with bus grant signal

Bus Master

- Bus request signal을 통해 bus transaction을 시작할 수 있다.

- CPU

- Main memory와 CPU register 사이 데이터를 이동한다.

- DMA controller

- CPU의 도움 없이 main memory와 I/O buffer 사이 데이터를 이동한다.

Bus Slave

- Bus master가 보낸 명령을 적절하게 수행한다.

- Memory controller(memory)

- Device Controller(I/O device)

I/O Operations

기본적으로 slave다. DMA 기능을 하는 device는 master의 역할도 한다.

Performed by “I/O Controller” under CPU command

- Register 보유

- Data register : Input/Output registers

- Control register : Control(CPU command 저장)/State(flow control에 사용) register

- I/O operation은 CPU가 개시한다.

- Output operation

- Status register를 확인해 output register 사용 가능 여부를 확인

- 가능하면 데이터를 output register에 운반하고, control register에 output command를 전달한다.

- 불가능하면 가능할 때까지 process를 반복하거나 기다린다.

- Polling or Interrupt-driven I/O

- Polling: 사용 할 수 있을 때 까지 기다린다.

- Interrupt-driven: 다른 작업을 하다가 사용 가능할 때 interrupt를 발생.

- Output operation

Two types of I/O addressing

- Memory-mapped I/O

- I/O register가 memory location에 할당.

- Memory와 I/O address가 같은 address bus를 사용.

- Input/Output을 위한 Load/Store

- Port-mapped I/O

- Port는 I/O controller 내부 register.

- I/O devices는 여기에 읽고 쓴다.

- 특별한 adapter가 중간에서 조율한다.

DMA(Direct Memory Access)

DMA

- Buffer storage와 main memory에 CPU의 개입 없이 device controller가 직접 데이터의 block을 전송할 수 있다.

- byte 단위가 아닌 block 단위로 interrupt가 발생한다.

- High-speed I/O devices가 memory에 정보를 빨리 전송하기 위해 쓴다.

2. Interrupt Mechanism

Interrupt는 asyn한 event를 알리는 역할을 한다.

Basics

Interrupt

- ISR(Interrupt Service Routine)에 제어를 넘기기 위한 “hardware mechanism.”

Types of Interrupts

- Hardware Interrupt

- Hardware signal로 발생한다.

- Async

- Software Interrupt(trap)

- Error나 instruction에 의해 발생한다.

- Sync

OS is interrupt driven

- Interrupt가 발생하면 OS가 control을 가져온다.

Interrupt Operation

Interrupt Mechanism

- At the time of Interrupt

- 프로그램을 중단한다. (PC 교체)

- 프로그램의 address를 저장한다. (Register 값을 stack memory에 저장)

- ISR에 맞는 IRQ(Interrupt ReQuest) number와 interrupt vector table(hashing table이다)의 주소를 가져온다.

- ISR로 jump한다.

- While Interrupt is being processed

- 우선순위가 같거나 낮은 Interrupt를 disable한다.

- After the execution of ISR

- 저장된 주소(중단된 프로그램)로 돌아간다.

Interrupt Hardware

Interrupt destination

- Microprocessor는 IRQ(input pin의 일종)를 가지고 있어 주의가 필요한 시스템 내부 다른 핀을 알 수 있다.

- Hardware의 signal로 Interrupt를 시작한다.

Interrupt source

- I/O chip은 service를 요청하기 위해 assert할 수 있는 pin을 가지고 있다.

PIC (Programmable Interrupt Controller)

Circuilt 내부 register 값 변경으로 동작을 바꿀 수 있다.

- Interrupt-driven system 환경 내부를 전반으로 관리한다.

- IRQ pins의 number보다 I/O devices를 지원한다.

PIC Operation

- IRQ lines로 signal 발생 여부를 확인한다.

- IRQ line에 signal이 발생하면 아래와 같이 동작한다.

- Signal을 받아 적절한 vector로 전환한다.

- Vector를 interrupt controller I/O port에 저장해 CPU data bus를 이용해 알아챌 수 있도록 한다.

- Processor에게 signal을 보내 interrupt를 발생한다.

- CPU가 PIC I/O port에 적힌 signal을 인식할 때까지 기다린다.

- 인식하면 INTER line을 정리한다.

- 다시 signal을 기다린다.

3. Hardware Protection Mechanisms

한 작업의 수행이 다른 작업들에 영향을 주지 않도록 한다.

Four Hardware Protection Mechanism

- Basic Mechanism : Dual mode operation

- I/O protection

- Memory protection

- CPU protection

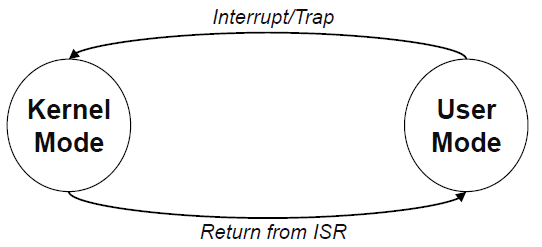

1. Dual Mode Operation

Motivation

- System resource 공유 시 OS는 다른 프로그램 간 간섭으로 부적절한 동작을 하지 못하도록 해야 한다!

Key Idea

- 최소 두 가지 mode로 hardware를 지원하자!

- User Mode

- User가 실행할 수 있다.

- Kernel Mode (System / Monitor mode)

- OS가 실행된다.

- Kernel mode 실행 중 OS는 kernel과 user memory에 무제한으로 access할 수 있다.

- User Mode

- PSR(Processor State Register) 내부 Mode bit이 추가된다.

- 0: kernel mode

- 1: User mode

- Interrupt나 trap이 발생하면 hardware는 kernel mode로 즉시 전환한다.

- Kernel mode에서만 동작하는 Privileged Instruction을 제공한다.

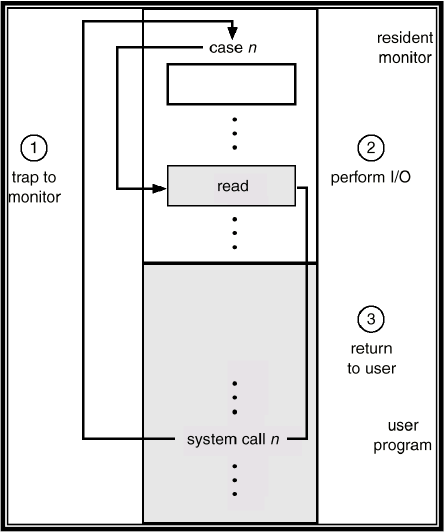

System call

- 사용자 프로그램이 kernel mode 내부 kernel function을 호출할 수 있는 방법.

- Mode의 전환이 일어난다.

- Function call과 비슷하다.

System call handling

2. I/O Protection

Motivation

- I/O devices 독점 방지.

Key Idea

I/O controller의 register는 user mode에서 접근이 불가능하다. Memory mapped I/O는 해당 memory를 protect한다.

- 모든 I/O Instruction은 privilaged Instruction이다!

- 사용자 프로그램이 kernel mode인 컴퓨터의 control을 절!대! 얻을 수 없다.

- 얻으려 하면 exception 발생

3. Memory Protection

Motivation

- 정의된 범위 밖에서 memory 접근 방지.

Key Idea

- 사용할 수 있는 address를 정의하기 위해 두 register 사용.

- Base register

- Bound register

- Base/Bound register를 load하는 것은 Privileged instruction이다.

4. CPU Protection

Motivation

- CPU가 독점 되는 것을 방지한다.

Key Idea

- OS가 control을 유지할 수 있도록 특정 주기마다 interrupt를 발생하는 timer를 만들자.

- Timer register를 만들어 해당 processor의 CPU 가용시간이 넘어가면 interrupt.

- Timer register를 load하는 것은 Privileged instruction이다.

This post is licensed under CC BY 4.0 by the author.